从单片 SoC 到多芯片系统的转变可以比作几十年前从手绘原理图到 RTL 和综合的转变。后者是通过电子设计自动化 (EDA) 技术实现的,该技术带来了软件和硬件解决方案,可实现芯片设计和验证流程的自动化。如今,芯片封装技术的进步以及 HBM3 和 UCIe 等行业标准的出现正在实现芯片的异构集成。

设计多芯片系统的主要挑战是什么?

在封装方面,根据性能、面积和连接性的优势,有多种类型可供选择,包括硅中介层、再分布层RDL中介层、扇出晶圆级封装和混合键合。

至于标准,它们有助于确保质量、一致性和互操作性。HBM3 提供高容量内存,防止 2.5D 多芯片设计中出现内存瓶颈。UCIe 正在迅速成为芯片间互连的事实上的标准,为小芯片的封装级集成提供带宽、低功耗和低延迟。

由于这些复杂系统的相互依赖性,开发多芯片系统所面临的挑战不断增加。

由于有如此多的互连组件,最好从系统范围的角度来考虑多芯片系统。同时解决系统、芯片和封装问题的协同优化方法有助于优化性能、功耗和成本。

但是,与任何复杂的系统一样,会出现许多问题:模具应该如何分割?最好使用什么类型的包装?您如何确保您的系统按预期运行?如何在严格的上市时间目标下开发这样的系统?等等。

多芯片系统架构中的每个决定和每个选择都必须考虑每个组件以及对系统整体功耗、性能和面积 (PPA) 目标的影响。多芯片系统设计团队通过整体方法共同解决所有挑战,从而产生******结果。毕竟,一个芯片散发的热量可能会影响旁边芯片的性能。

同样,前端逻辑设计中发生的情况必须考虑到后端物理设计。如果没有整体方法,工程师将面临耗时且成本高昂的迭代的风险。

多芯片系统的未来发展方向

随着半导体领域的不断发展,设计团队显然需要能够应对多芯片系统架构独特挑战的流程和工具。在这一领域,将不同的设计和验证工具拼接在一起是行不通的。最终目标仍然与单片系统级芯片类似:团队希望优化 PPA,同时提高生产率并实现上市目标。

考虑到多芯片系统的多维性,我们需要的是一个全面而有凝聚力的解决方案,它能够扩展和优化,以处理这些类型设计的复杂性。理想的解决方案可以实现早期架构探索、快速软件开发和验证、高效的芯片/封装协同设计、稳健安全的芯片到芯片连接,以及改善系统的健康状况和可靠性。

要实现多芯片系统的前景,其开发过程必须具有整体性,考虑到这类芯片架构固有的所有相互依存关系。

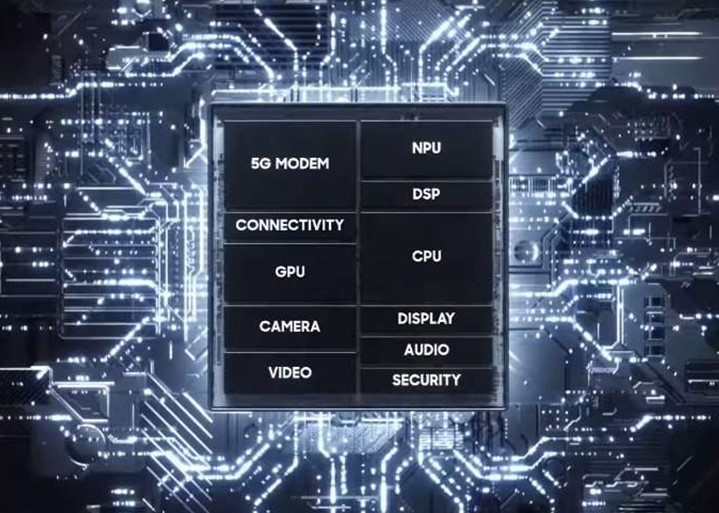

在元宇宙中的每一次身临其境的逍遥游、汽车能够独立执行的每一次功能、机器能够预测你可能想要的每一次功能,底层系统都在要求内部的硅芯片实时提供大量的功能。虚拟现实/增强现实、自动驾驶汽车和人工智能等计算密集型应用对性能、带宽和面积的要求将越来越高。

···

···

···

···

···

···

···

···

···

···

···

···

···

···

···